| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 시계열 데이터

- scikitlearn

- LogisticRegression

- Python

- GridSearchCV

- DataScience

- 딥러닝

- 잔차분석

- 의사결정나무

- time series

- 분류

- 선형회귀분석

- 데이터전처리

- 다중선형회귀분석

- ML

- machinelearning

- 지도학습

- 단순선형회귀분석

- 결정계수

- dataframe

- 하이퍼파라미터

- LinearRegression

- 데이터분석

- 손실함수

- 로지스틱회귀분석

- 시계열데이터

- RegressionTree

- OrdinalEncoder

- deeplearning

- 비지도학습

- Today

- Total

IE가 어른이 되기까지

[반도체 공정 및 장비] Metal (배선) 본문

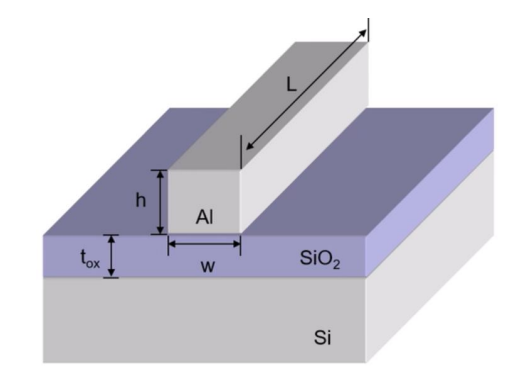

우리는 반도체를 만드는 데에 있어서 전기적인 신호를 흘려줄 금속이 필요합니다.

Metal의 기능

이러한 Metal은 외부와의 전류와 전압을 흘려주기 위한 Contact 역할도 수행하고

개별적인 소자와 소자들을 연결시켜주는 Interconnection로서의 역할도 수행합니다.

또한, Chip을 만들고 나서 Board나 외부 제품과 연결하는 Connection to Outside의 역할도 하는데요

Metal이 갖추어야하는 요건

이러한 Metal System이 갖추어야할 요건에는 무엇이 있을까요 ?

1. 공정 적합성과 용이성

먼저 Metal은 원하는 형태대로 Patterning 되기 위해 Etch 공정이 잘 이루어져야하고 Selectivity가 높아야합니다.

또한, 다른 소자들과 연결해주기 위해 인접한 Insulator(산화막)와의 접착성이 좋아야하는데,

이때 Contact 형태가 Ohmic Contact 인 것이 좋습니다.

마지막으로 Metal은 부피변화가 크기 때문에 온도가 바뀌는 과정에서

끊어지거나 빠져나올 수 있으므로 안정적인 물질이 필요합니다.

2. 전기적인 조건

Metal은 소자와 소자 사이에 전류를 흘려주는 것이기 때문에 저항이 낮아야하고 전도도가 높아야합니다.

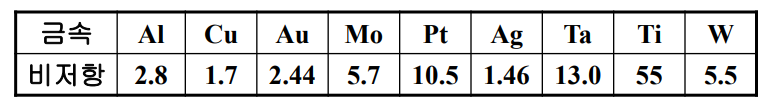

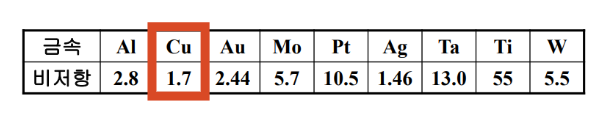

과거에는 Metal로서 비저항도 비교적 낮고 Etch도 잘되는 Al(알루미늄)을 사용하였습니다.

하지만 Metal Line이 점점 복잡해지고 좁아지면서

이정도 비저항으로는 부족해졌는데요, 그렇게 현재는 Cu(구리)를 사용하는 추세입니다.

이러한 Cu는 Dry Etch가 불가능해서 CMP를 사용해야한다는 특징이 있습니다.

다른 Metal에 대해서도 알아보자면 Ag(은)는 비저항은 낮지만 Electromigration,

즉 전류가 많이 흘렀을 때 전자들이 충돌하면서 Grain 덩어리들이 떨어져나가게 되는 현상이 발생합니다.

W(텅스텐)는 비저항은 높지만 CVD가 가능해서 좁은 부분을 채우는 데 유리하므로

Contact 부분에만 채우는 데에 사용합니다.

3. 신뢰성

Metal의 경우 좁은 부분을 잘 채워야하므로 앞서 언급하였던 Electromigration이 좋아야합니다.

또한, 동작을 하면서 발생하는 열에 의해 끊어지면 안되므로 열적, 화학적으로 안정된 상태를 요구합니다.

Metal Film 형성 방법

Metal Film을 형성하는 방법에는

앞선 글에서도 알아봤었던 CVD, PVD 방식이 존재합니다.

CVD (Chemical Vapor Deposition)

CVD는 화학적인 방식으로 기체 분자를 증착시키는 방법인데요

위치에 관계없이 위와 측벽에 고른 증착이 가능해

Uniformity와 Step Coverage가 높다는 장점이 있습니다.

하지만 소자의 Size가 작아지면서 Trench 구조의 측벽을 덮기 어려워져

W(텅스텐)만 CVD룰 활용하는 추세입니다.

PVD (Physical Vapor Deposition)

PVD는 물리적 방법으로 증착시키는 방법인데, 이를 Evaporation과 Sputtering으로 나눌 수 있습니다.

Evporation 방식의 경우 Metal 소스를 가열해 기화시킴으로써

반대 웨이퍼에 원하는 Metal을 증착하는 방식입니다.

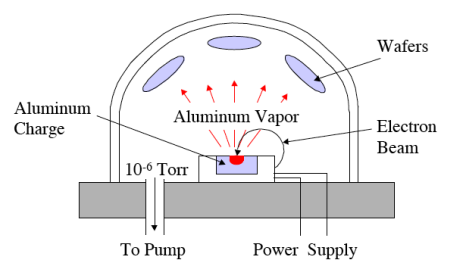

Evaporation 방식은 Chamber 안에 가열될 수 있는 Filament를 매달아놓는 Filament Evaporation,

기화시킬 물질 주변에 RF Coil을 감아놓고 RF에 의해 열을 가하는 RF Evaporation,

Electron Beam으로 소스 표면을 때리는 E-beam Evaporation으로 나뉩니다.

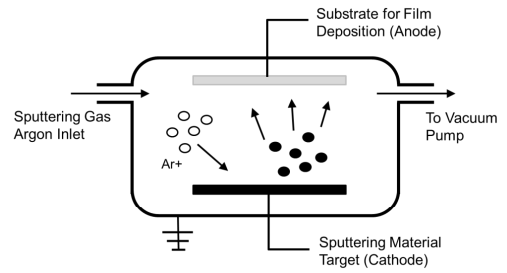

Sputtering 방식은 에너지를 가진 이온이 Metal 소스 표면을 때려서 뜯어내는 방법입니다.

Evaporation이 되지 않는 Metal에 대한 증착이 가능하지만 증착 속도가 느리다는 단점이 있습니다.

PVD는 비교적 Step Coverage가 낮은데요,

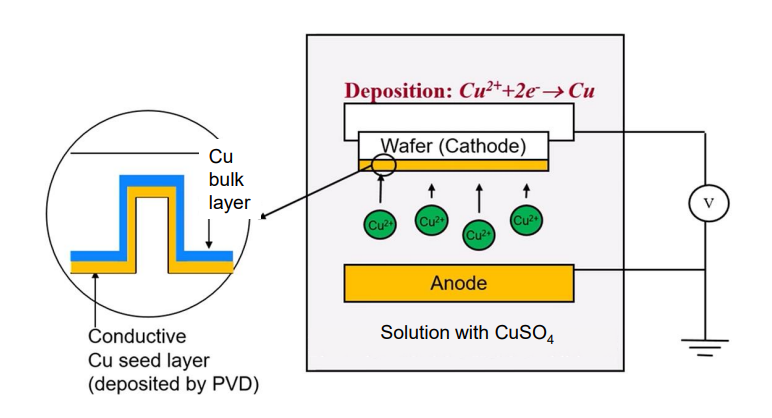

이를 해결하기위해 PVD를 먼저 얇게 덮은 후 Electroplating 방식을 사용합니다.

Electroplating은 위 그림처럼 웨이퍼를 Cathode에 붙여놓고 Cu가 녹아있는 Solution에 담가놓은 후,

웨이퍼 쪽에 Negative Bias를 걸면 Cu가 웨이퍼로 이동해서 Seed 위로 성장하는 구조입니다.

Metal 종류

Al (알루미늄)

소자가 작아지면서 소스와 드레인이 Gate를 빗나가는 것에 대한 영향이 커지면서

Gate에 맞춰 Ion Implantation을 진행함으로써 소스와 드레인이 자동적으로 정렬되게끔 하였습니다.

기존에는 이러한 Gate 물질로 Al(알루미늄)을 가장 많이 사용했었습니다.

Al은 저렴하고 비교적 전도도가 높으며 Contact 저항이 낮고 Dry Etch가 가능해 Patterning이 용이합니다.

하지만 CVD가 되지 않아 부식이 잘된다는 단점과

Ion Implantation의 Annealing 과정에서 녹아버린다는 문제점이 존재합니다.

이에 최근에는 Gate를 마지막에 Metal로 갈아끼워주는 Gate Last, RMG(Replacement Metal Gate)를 사용합니다.

특히 Gate로 Al을 사용하면 다음과 같은 2가지 특성이 발생하곤 하는데요

첫번째는 Junction Spike입니다.

이는 Al이 Si와 반응함으로써 원치 않는 부분까지 파고 들어가

소스와 드레인 이외의 Substrate과도 반응해 Short가 발생하는 것으로

를 방지하고자 소량의 Si를 섞어줍니다.

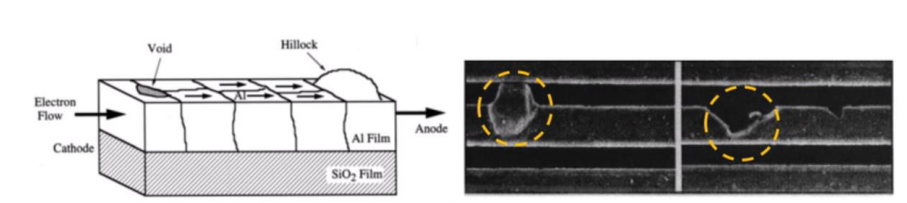

두번째는 Electromigration 현상입니다.

Metal를 덮으면 부분적으로 결정화가 되고 나머지는 Grain 상태로 덮이게 되는데

이러한 Metal Line에 전류를 흘려주면 Electron과 Grain들이 충돌을 하게 되어서

Electron의 Density가 높아지는 바람에 Grain이 떨어져나가거나 튀어나오게 됩니다.

이러한 현상을 Electromigration이라고 정의하고, 이를 해결하고자 소량의 Cu를 섞어줍니다.

W (텅스텐)

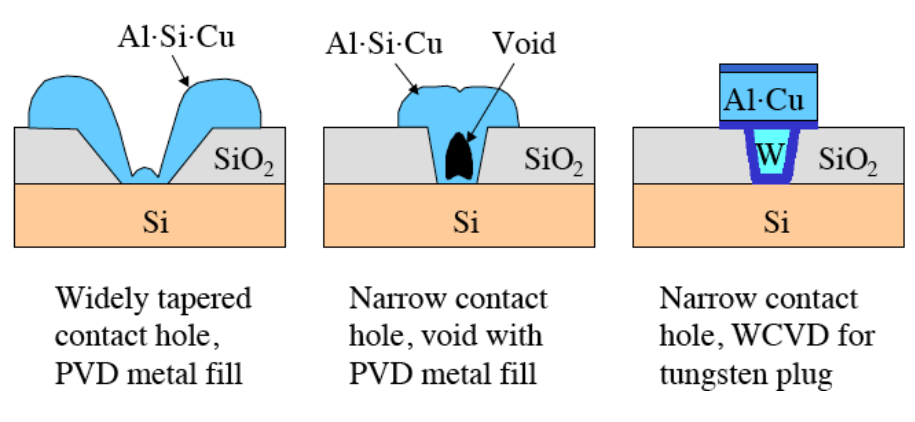

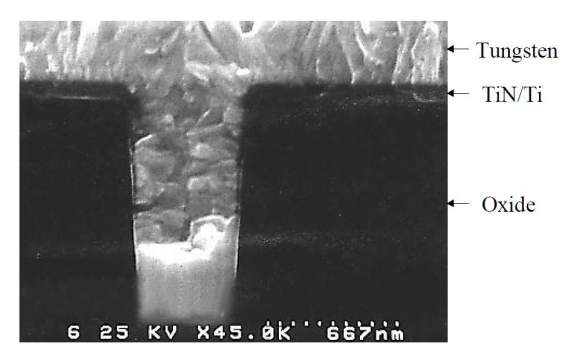

W(텅스텐)는 유일히 CVD가 가능한 Metal 물질입니다.

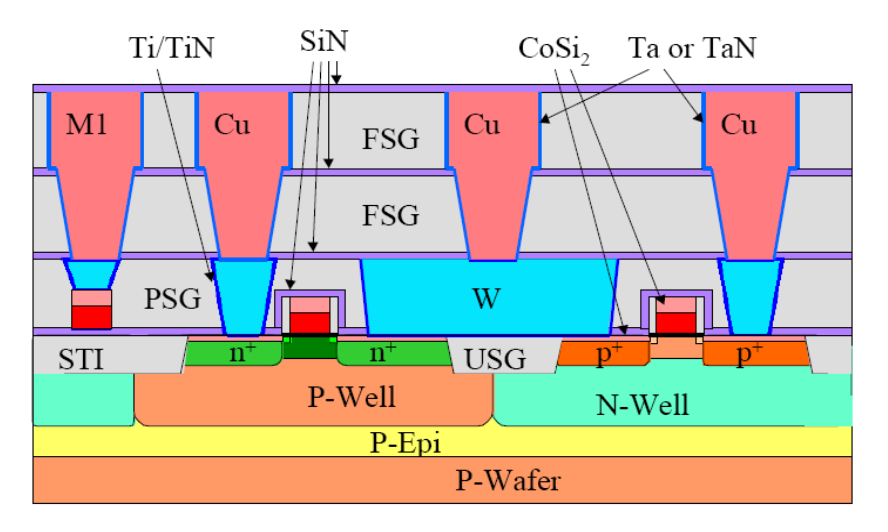

Metal의 Contact(실리콘 소자와 바로 맞닿는 부분) 부분과 Via(Metal과 Metal 사이를 연결해주는 Hole)는

PVD로는 Step Coverage가 좋지 않아 Void가 발생할 수 있으므로

CVD가 가능한 W를 사용하곤 합니다.

하지만 저항이 크다는 단점이 존재하여 선택적으로 사용하게 됩니다.

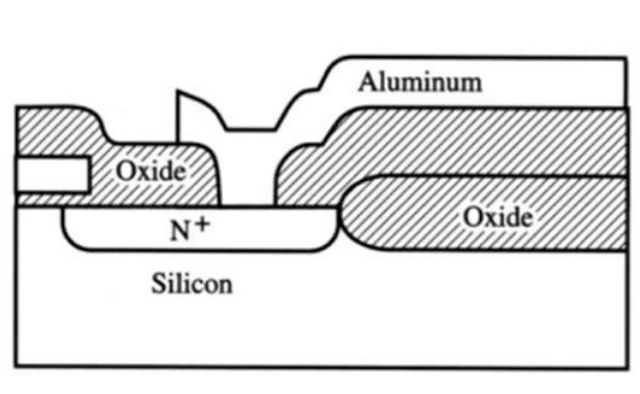

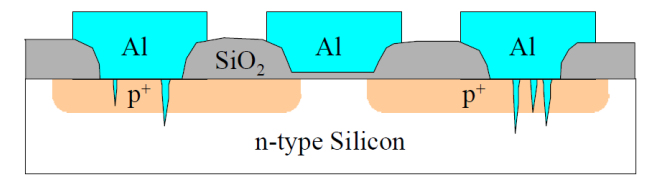

왼쪽 그림처럼 큰 Pattern에서는 Al을 PVD로 덮어도 채워지는데,

Pattern이 점차 작아지면서 Void가 발생하고 아예 끊어지면서 W(텅스텐)을 선택적으로 사용하게 됩니다.

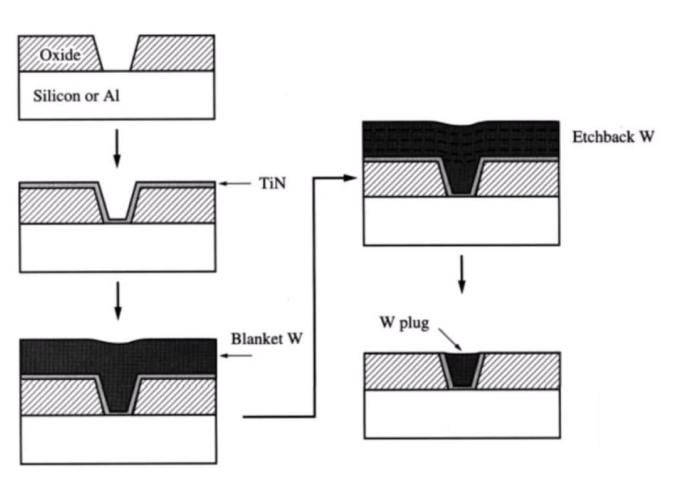

하지만 W은 Cu나 Oxide와 잘 붙지 않고 Oxide와 Si으로 잘 Diffusion 되기도 해서

Barrier 및 Adhesion Metal(TiN)을 사용해서 W을 덮고 평평하게 갈아주는 방식을 사용합니다.

Cu (구리)

Cu(구리)는 Al보다 저항이 낮고 Electromigration이 좋은 물질입니다.

그동안은 Dry Etch가 어려워서 사용하지 않았는데 CMP로 패턴을 만들기 시작한 이후로는 주로 사용되곤 합니다.

하지만 SiO2와 잘 달라붙지 않는다는 점과 SiO2 쪽으로 잘 파고든다는 단점이 있어

Barrier 및 Adhesion Metal(TiN)을 덮음으로써 해결해줍니다.

Metal 공정 주요 요소

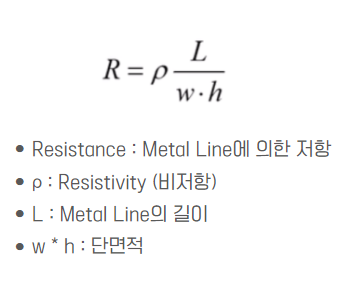

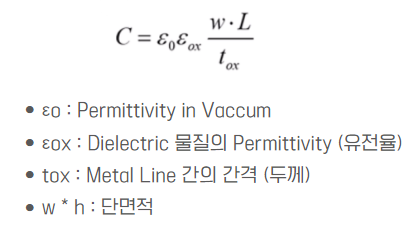

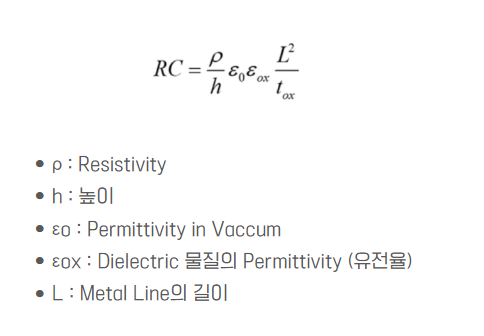

1. RC Delay

RC Dealy란 R(저항, Resistance)와 C(전기용량, Capacitance)를 곱한 값으로

전기 신호 전달 속도의 지연을 의미합니다.

당연히 전기 신호 전달의 속도가 빨라야 그만큼 소자의 성능이 좋다는 의미이겠지요 ?

RC Dealy에서의 Resistance는 물질의 Resistivity와 Metal Line의 길이에 의해 결정이 되고

Capacitance는 Dielectric 물질의 Permittivitiy와 Metal Line끼리 인접하고 있는 면적,

그리고 Metal Line 간의 간격, 즉 두께에 의해 결정됩니다.

그렇게 앞서 살펴본 R과 C의 곱에 의해 Metal Line에 의한 Time Delay가 결정됩니다.

즉, 이러한 R과 C를 줄여야 Time Delay가 줄어들겠지요 !

하지만 최근 제품을 만들 때 한꺼번에 많은 소자를 넣다보니 L이 길어짐에 따라 Time Delay도 증가하기 때문에

Resistivity가 작은 물질을 사용하고자 Metal 물질로서 Al보단 Cu를 사용하게 되었으며

Capacitance를 줄이고자 Metal 사이의 Permittivity를 줄이는 노력이 필요해졌습니다.

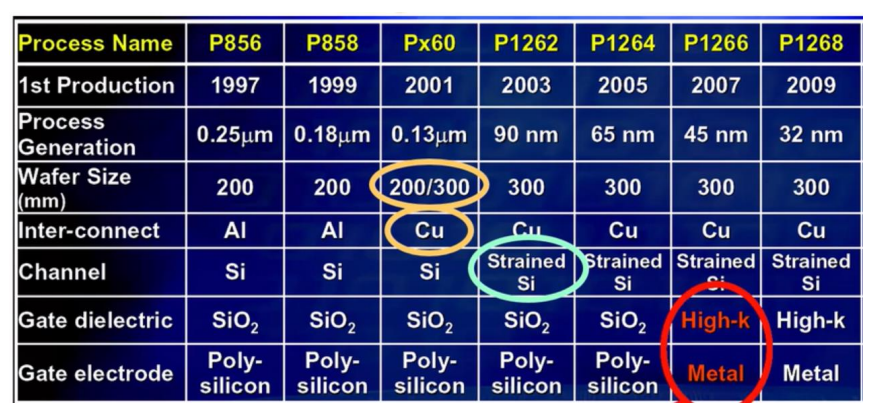

위 그림처럼 180nm 공정까지는 Metal(Inter-connection)로 Al에서 Cu를 사용하기 시작하였고

Channel로 Silicon을 그대로 쓰기 보다는 PMOS, NMOS에 따라

적당한 Strain(스트레스)를 가해줌으로써 Mobility를 향상시키고자 하였습니다.

또한, 45nm 공정부터는 물리적으로 Gate Dielectric 두께를 줄이는 것이

Leakage 부분에서 한계가 존재하여 Permittivity가 낮은 High-k를 사용하게 되었고

Gate 부분의 저항을 줄이고자 Poly-Silicon에서 Gate Last, RMG라는 공정을 사용하기 시작했습니다.

2. Barrier & Adhesion Layer

W와 Cu는 Si에 맞닿게 되면 다음과 같은 두가지 문제가 생깁니다.

먼저, Channel 쪽으로 쉽게 Diffusion 되면서 소자에 Leakage나 여러 문제가 발생하고

인접하고 있는 Oxide하고 잘 달라붙지 않는다는 문제점이 발생합니다.

이에 Metal을 채우기 전에 Diffusion을 막아줄 수 있는 Layer로서

Ti, TiN, Ta, TaN을 미리 얇게 깔아두는 방식을 사용합니다.

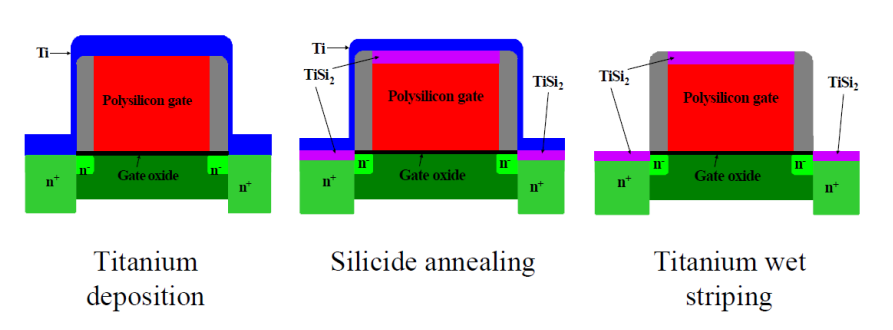

3. Silicide

Silicide는 실리콘과 금속의 화합물로서,

금속-반도체 접합에 비해 화학적으로 안정하고 낮은 접촉저항을 가집니다.

대표적으로 WSi2, MoSi2, TiSi2, CoSi2등이 있습니다.

Metal을 형성하기 전에 Ti나 Co, Ni로 덮어준 다음 열을 가해주게 되면

소스, 드레인, Gate 표면 부분이 Silicide로 변경됩니다.

그 후, 남은 Metal 부분을 Wet Etch로 제거해주면 표면에 낮은 저항이 만들어져서 저항을 줄일 수 있게 됩니다.

이러한 과정에서 Gate와 소스 및 드레인 간의 Short 발생을 막아주고자 Spacer라는 것이 존재합니다.

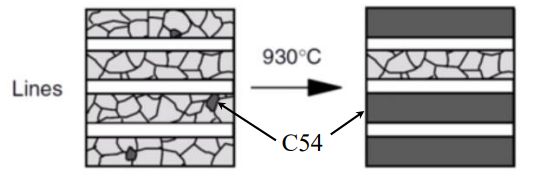

특히 Ti Silicide에서의 C54 형태의 Silicide는 부분적으로만 존재하는 낮은 저항의 물질로

두번째 Annealing 과정을 거치면 이를 Seed로 삼아 근접한 부분도 낮은 비저항을 띄게 됩니다.

하지만 소자가 작아지면서 이러한 C54 Seed가 존재하지 않을 확률이 증가하면서 CO, Ni Silicide를 사용하는 추세입니다.

이번 글에서는 반도체에 전기적인 특성을 가해주는 Metal 공정에 대해 알아보았는데요,

마지막 글에서는 CMP에 대해 다뤄보겠습니다.

'SEMICONDUCTOR' 카테고리의 다른 글

| [반도체 공정 및 장비] CMP (Chemical Mechanical Polishing) (2) | 2024.03.19 |

|---|---|

| [반도체 공정 및 장비] Etch (식각) (0) | 2024.03.18 |

| [반도체 공정 및 장비] Photolithography (포토) (1) | 2024.03.14 |

| [반도체 공정 및 장비] CVD (화학 기상 증착, Deposition) (0) | 2024.03.14 |

| [반도체 공정 및 장비] PVD (물리 기상 증착, Deposition) (0) | 2024.03.13 |